文章编号:1005-0523(2010)06-0047-05

# 基于 FPGA 的 MVBC 帧收发器设计

# 丁青锋,朱其新,幸柒荣,魏耀南

(华东交通大学 电气与电子工程学院,江西 南昌 330013)

摘要:首先分析了多功能车辆总线(multifunction vehicle bus, MVB)的通信机制与特点,在此基础上,采用 VHDL 语言编写了 MVB 总线控制器(MVB controller, MVBC)帧收发器中曼彻斯特编译码、循环冗余码校验(cychinc reduncy check, CRC)校验等核心功能的算法,设计了收发器中发送模块和接收模块;最后 FPGA 实现了 MVB 主、从数据帧的收发。

关键词:多功能车辆总线控制器;FPGA;循环冗余码校验;曼彻斯特编译码

中图分类号:U<sup>285</sup>

文献标识码:A

基于分布式控制的 MVB 是 IEC61375—1(1999)TCN(列车通信网络国际标准)的推荐方案,它与绞线式列车总线(WTB)构成的列车通信总线具有实时性强、可靠性高的特点[1]。而 MVBC 是实现 MVB 总线网络功能的关键器件,负责访问 MVB 总线并提供与微处理器的通信接口,实现数据传输[2]。

总线与 MVBC 之间数据通信在 MVBC 中由帧收发器来完成,包括编码/译码模块、CRC 校验模块以及 发送接收控制模块等。目前 MVB 的收发器采用专用芯片 MVBC 实现,但随着片上系统技术的发展,现代 电子设计趋向高度集成化,因此类似的接口芯片大都已经被 ASIC (application specific integrated circuit)的软 核替代<sup>[3]</sup>。本设计中采用 FPGA 开发 MVB 的帧收发模块作为 MVB 控制器的一个软核。

## 1 MVBC 简介

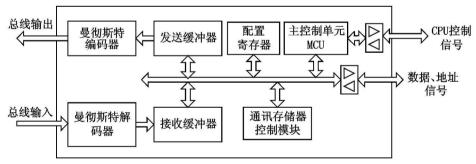

MVBC 在数据链路层上处理帧的接收与发送,依靠物理层发送和接收具有电气特征的电信号;同时为网络层提供过程数据、消息数据的变量接口,该接口采用通讯存储器实现。图 1 为本项目设计的 MVBC 内部结构框图,由曼彻斯特编解码模块、发送/接收缓冲器、配置寄存器、通讯存储器(TM)以及主控制单元等部分组成。

图 1 MVBC 结构框图

MVBC 通过物理层提供的双线冗余连接 MVB,接收 CPU 的访问控制,从而实现 MVB 上获取和发送设备数据,同时通过访问监视数据实现对 MVB 的管理。

发送数据时, MCU 将帧数据从 TM 读出并写到发送缓冲器中, 再由编码器读出并完成编码校验等功能后发送到 MVB 总线上;接收时解码器完成对输入帧译码并检验其有效性, 把数据存放到相应的通讯存储

收稿日期:2010-10-28

**基金项目**:国家自然科学资助项目(60964004);华东交通大学科研基金资助(10dq02)

**作者简介**:丁青峰(1980—),男,讲师,硕士,研究方向为计算机通信与网络研究。 (C)1994-2024 China Academic Journal Electronic Publishing House. All rights reserved. http://www.cnki.net 器中,从而完成接收数据的过程。另外,MVBC可根据配置实现总线主与总线从的功能,实现数据链路层以及一部分传输层的数据处理,并通过通讯存储器来与上层软件交互。

## 2 帧收发器的设计

MVBC 中的帧收发器主要负责帧的发送、接收,包括曼彻斯特的编码、译码,CRC 的产生与校验,不同类型帧的构建与识别,以及码错的识别和冲突的检测等。其中曼彻斯特编译码以及 CRC 校验为主要的算法。

## 2.1 曼彻斯特编码实现

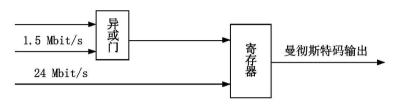

曼彻斯特编码单元主要是完成主、从帧数据的编码,其结构如图 2 所示[9]。

图 2 曼彻斯特编码原理图

由数据并串转换单元、CRC 生成单元和帧分界符单元经多路选择器产生的串行数据与 1.5 MHz 的 16 分频时钟 clk-16div 进行异或, 然后在 24 MHz 的系统时钟 clk 的上升沿通过一个一阶寄存器后再将已编码的数据输出。虽然这样要比串行输入晚一个时钟周期, 但却保证了输出信号的稳定。

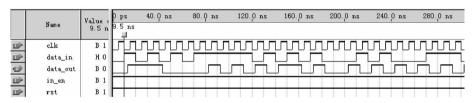

曼彻斯特编码<sup>[4-5]</sup>是在曼彻斯特编码中,每一位的中间有一跳变,位中间的跳变既作时钟信号,又作数据信号;从高到低跳变表示"1",从低到高跳变表示"0"。该码型具有丰富的定时信息、无直流分量等优点,特别适合于多路数据的快速切换。图 3 是使用 QuartusII 实现曼彻斯特编码波形。

图 3 曼彻斯特编码仿真波形

因帧头、帧尾不是曼彻斯特编码,因此传统的曼彻斯特编译码器无法完成此项工作,需要采用结合收发器状态机具体状态进行编译码的设计方法来解决这一难题<sup>[3]</sup>。

## 2.2 曼彻斯特译码实现

对于译码模块来说,同步检测是关键。只有检测到同步信息,才开始译码周期。当曼彻斯特译码采用 FPGA 实现时,采用对沿的判断来实现:上升沿为0,下降沿为1。

前面已经说明, MVB 链路层数据是以帧为基本单位,一帧数据分为帧头、数据和帧尾。帧分为主帧和从帧,帧头采用不同的编码,帧尾为 0.75 BT + 125 ns 的低电平,而数据采用曼彻斯特编码。译码器检测线路起始位,判断帧头数据正确后,对其后的曼彻斯特数据进行译码,并将其转换为正常的逻辑数据,送给控制逻辑。

曼彻斯特编码输入后经过三级寄存器同步消除亚稳态。如果总线在空闲状态之后出现下降沿,则被认为帧的开始位,总线上再出现高电平时使能 16 位计数器计数。如果把曼彻斯特编码每个 bit 周期分为 16 个部分。则在数据采样 1 处得到的采样值即为曼彻斯特编码前的原数据,数据采样 2 处用来帧头帧尾检测;总线冲突检测的原则为总线上曼彻斯特编码的半个 bit 周期之内的电平应一致,前后半个周期电平应相异,否则被认为码错。

(C)1994-2024 China Academic Journal Electronic Publishing House. All rights reserved. http://www.cnki.net

#### 2.3 数据校验

在 TCN 协议中,对数据需要进行两种 CRC 校验和奇偶校验。在国际标准中,根据生成多项式 g(x)的 不同,CRC 又可分为几种标准<sup>[3]</sup>。本文中 7 位 CRC 校验码的运算公式遵循 IEC 60870-5 format class FT 2 的 规定,按如下的生成多项式计算:  $g(x) = x^7 + x^6 + x^5 + x^2 + 1$ ,通过数据表达式支除生成多项式得到 CRC 校验码。CRC 校验方式分为串行和并行两种,串行方式简单但是耗时较长,而并行方式算法复杂但只适合等长信息位校验。由于 MVB 中帧数据长度是不断变化的,但帧数据长度较短,因此本文采用串行方式。

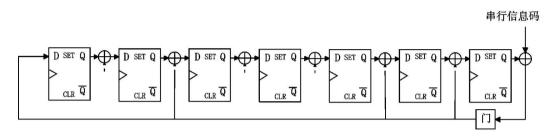

CRC 校验码生成电路采用线性反馈移位寄存器来实现,也就是通用的 CRC 串行算法实现电路。如图  $4~\rm M\pi$ 。每一个 D 触发器保存一位码元数据 $^{[5-6]}$ 。

图 4 CRC 原理图

图 4 中, 寄存器通过异或门连接, 当有与门连接时取反; 没有连接时直接将上一个寄存器输入到下一个寄存器。其中, "门"用来控制信息码的输入。门打开时信息码输入; 当信息码元全部输入完毕时, 门关闭, 禁止任何码元输入, 此时 7 个寄存器中所存放的 7 位码元就是得到的校验位。

其次,再对 7 位 CRC 校验码进行偶校验。根据偶校验原理,偶校验位  $a_0$ 计算公式如下:  $a_0 = a_1 \oplus a_2 \oplus a_3 \oplus a_4 \oplus a_5 \oplus a_6 \oplus a_7$ 。其中  $a_1$ ,  $a_2 \oplus a_3 \oplus a_6 \oplus a_7$ 。其中  $a_1$ ,  $a_2 \oplus a_3 \oplus a_6 \oplus a_6 \oplus a_7$ 。其中  $a_1$ ,  $a_2 \oplus a_3 \oplus a_6 \oplus a_6 \oplus a_6 \oplus a_7$ 。其中  $a_1$ ,  $a_2 \oplus a_3 \oplus a_6 \oplus a_6$

最后,所有8位数据取反得最终校验序列。

# 3 总线接口模块的设计实现

总线接口模块包括发送模块和接收模块

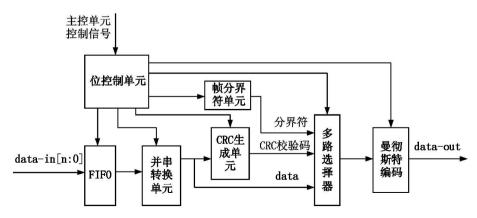

## 3.1 发送模块

发送模块主要在主控单元的控制下完成主、从帧数据的曼彻斯特编码,打包以及相应校验序列的产生和发送。发送模块由发送控制单元、帧分界符单元、数据并串转换单元、CRC生成单元、FIFO(first-in first-out)单元、多路选择器单元和曼彻斯特编码单元组成。整个模块是通过状态机完成,其内部结构图如图 5 所示[9]。

图 5 发送模块结构图

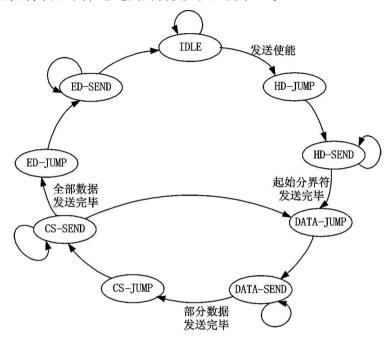

发送模块中除上述 CRC 生成单元、曼彻斯特编码单元等之外,位控制模块是整个发送模块的核心,在系统复位或者前一帧发送完毕后将进入 IDLE 状态,等待发送使能信号;然后启动发送起始分界符;在发送完分界符后启动计数器开始发送数据,每发送 16 位数据,字计数变量 word-counter 加 1;将校验序列生成单元计算出的校验序列发送到曼彻斯特编码单元;判断应发送的帧数据字数与变量 word-counter 的值是否相等,相等则进入终止分界符生成状态,否则继续发送数据,直到到发送完数据为止。本设计采用有限状态机的方式来实现发送控制单元,其状态之间的转换如图 6 所示<sup>[10]</sup>。

图 6 发送控制单元状态转换图

其中 HD-Jump, DATA-Jump, CS-Jump, ED-Jump 四个状态为过渡状态, IDLE 为空闲等待状态, HD-SEND, DATD-SEND, CS-SEND, ED-SEND 四个状态分别为起始分界符、数据、CRC 校验码以及结束分界符的发送状态。

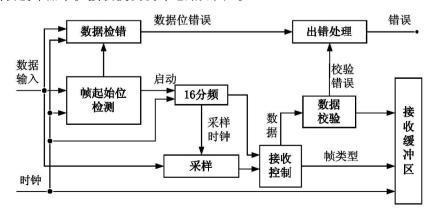

#### 3.2 接收模块

MVB 总线采用冗余介质,因此 MVBC 需要冗余的接收模块来完成帧的接收。接收模块的功能主要有以下几个:完成对帧数据的其始位判定、数据采样、数据译码和数据移位功能;判断帧数据类型,从帧中提取数据并存入接收缓冲器中。接收模块设计电路如图 7。

图 7 接收模块结构图

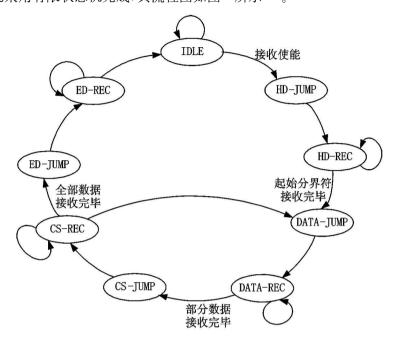

在接收帧的同时,译码器将是否接到帧、何种帧类型、接收是否完成、结果对错等信息告诉线路控制模 块,该模块将这些信息与接收缓冲器有效上报至上层模块进行报文分析。控制模块从接收状态来验证帧 的属性:帧是否有效、帧类型、帧长度,并从读出的数据来验证数据的正确性[9]。其中接收控制单元是接收 模块的核心,其实现采用有限状态机完成,其流程图如图 8 所示[10]。

图 8 接收控制单元状态转换图

其中 HD-REC, DATA-REC, CS-REC, ED-REC 分别为起始分界符、校验位以及结束分界符的接收状态。

## 结束语

随着我国高速铁路的迅猛发展,TCN 在动车组上已开始逐步得到应用,我国自行研制生产的 CRH。的 列车网络控制系统的网络架构就是采用了 TCN 标准。TCN 网络的广泛应用也给了 MVBC 巨大的市场前 景。本文主要介绍 MVBC 与 MVB 总线接口部分的帧收发器中各模块的算法分析、设计实现。通过对各模 块进行的 FPGA 验证, 充分论证了该设计方案的可行性。

#### 参考文献:

- [1] HUANG ZHIWU, ZHOU SHENG, CUI WEIHUA, et al., Research and design of protocol analyzer for multifunction vehicle bus [C]//in Proceedings of the 7th World Congress on intelligent Control and Automation, 2008;8358-8361.

- [2] 黄采伦, 樊晓平, 陈特放. 列车故障在线诊断技术及应用[M]. 北京: 国防工业出版社, 2006: 212-229.

- [3] 侯宁,丁荣军,王永翔,等. MVB 网卡的帧收发器设计[J]. 机车电传动, 2006(1): 19-22.

- [4] 蔡颖,诸昌钤. MVB 网络接口单元的 FPGA 实现[J]. 铁道机车车辆, 2005, 25(3): 26-70.

- [5] 金素梅,王家礼.基于 FPGA 的 CRC 编码器的实现[J]. 现代电子技术, 2005, (24): 18-22.

- [6] 张树刚, 张遂南, 黄士坦. CRC 校验码并行计算的 FPGA 实现[J]. 计算机技术与发展, 2007(2): 26-62.

- [7] 江文丹, 董显, 薛红岩, 等. 基于 VHDL 语言的多功能车辆总线编码器设计与分析[J]. 铁路通信信号工程技术, 2008(10), 9-12.

- [8] 付林,任志平,刘承杰,基于 FPGA 技术曼彻斯特编码器设计[J].现代电子技术,2007(17):55-59.

- [9] 幸柒荣. 基于 FPGA 的 MVB2 类设备控制器设计[D]. 南昌: 华东交通大学, 2009.

- [10] 魏耀南· MVB 四类设备网络接口设计及实现[D]· 南昌: 华东交通大学, 2010.

#### 参考文献:

- [1] 陈爽, 杨军. 粒径对油溶性 Cu 纳米颗粒抗磨性能的影响[J]. 润滑与密封, 2010, 35(1), 75-77.

- [2] 沃恒洲,魏泽峰,刘淑丽,等.纳米润滑添加剂的摩擦学特性[J].合成润滑材料,2010,37(1):22-25.

- [3] 张二水. 高碱磺酸盐型极压剂的性能及应用[J]. 润滑油, 2001, 16(5): 40-45.

- [4] 王辉·烷基吩噻嗪的合成及在润滑油中抗氧化性能的研究[D]·大连:大连理工大学,2009.

- [5] 薛艳, 姚俊兵. 有机碱金属盐抗氧协和剂在合成润滑油中的应用[J]. 润滑油, 2005, 20(1), 30-33.

- [6] 姚文钊,付兴国,刘雨花,等.中碱值烷基水杨酸钙的新型制备技术及产品性能研究[J].润滑油,2008,23(6):46-51.

- [7] 何忠义,熊丽萍,徐欢,等.一种双杂环衍生物的摩擦学性能研究[J].润滑油与燃料,2010,20(213):22-25.

- [8] WAGNER C D. Handbook of X-ray photoelectron spectroscopy [M]. Perkin-Elmer, Physical Electronic Division, MI. 1979.

- [9] HONG H, RIGA AT, CAHOON J M, VINCI J N. Evaluation of overbased sulfonates as extreme pressure additives in metalworking fluids [J]. Lubrication Engineering, 1993, 49(1):19-24.

# On Tribological and Oxidation Properties of Alkali Metal Sulfonate-modified Nano Carbonate

Xiong Liping<sup>1</sup>, Wang Junxiao<sup>1</sup>, He Zhongyi<sup>1,2</sup>, Qiu Jianwei<sup>2</sup>, Fu Xisheng<sup>2</sup>

$(1\cdot School\ of\ Basic\ Sciences, East\ China\ Jiaotong\ University, Nanchang\ 330013, China;\ 2\cdot PetroChina\ Lanzhou\ Lubricating\ Oil\ Research\ and\ Developing\ Institute, Lanzhou\ 730060, China)$

Abstract: The tribological properties of amiddle base value sulfonate modified double nucleus nano carbonate alkali metal as lubricating oil additive are introduced in this paper, and its antioxidant collaboration property with ashless antioxidant is evaluated by using Rotary Bomb Oxidation Test (RBOT). The results show that the product possesses good tribological properties, and a good synergistic antioxidation effect with ashless antioxidant.

Key words: alkali metal sulfonate; nano carbonate; tribological property; antioxidant

(责任编辑 刘棉玲)

(上接第51页)

# Design of MVBC Frame Transceiver Based on FPGA

Ding Qingfeng, Zhu Qixin, Xing Qirong, Wei Yaonan

(School of Electrical and Electronic Engineering, East China Jiaotong University, Nanchang 330013, China)

Abstract: This paper introduces the MVB bus communication mechanisms and characteristics. On this basis, the algorithm of the MVBC frame transceiver core functions, such as Manchester encoding and decoding (CODEC), CRC checking and so on, has been described by the VHDL language; transmitter module and receiver module has been designed. Finally, the receiving and transmission of MVB Master Frame and Slave Frame has been realized on FPGA.

Key words: MVBC; FPGA; CRC; Manchester encoding and decoding

(责任编辑 刘棉玲)