# 用 GAL16V8 实现模 2~64 可变计数器

# 裴 亚 男

(电气工程系)

摘 要 简单介绍了测周模式的测频原理,着重介绍用 GAL 可编程器件设计、编程模可 变计数器,以代替测周模式测频装置中的定标器.

关键词 计数器;模;分频

分类号 TN791

# 0 引言

现代科学技术对电子测量提出了更高的要求. 在电子技术领域内, 频率是一个最基本的参数, 频率与其他许多电参量的测量方案、测量结果都有十分密切的关系. 因此, 如何提高频率的测量精度显得非常重要.

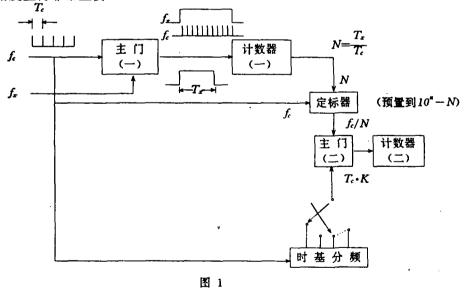

在被测信号频率较低时,为了提高测量精确度,一般采用测周模式的测频方法.设时基频

收稿日期:1995-05-03.

裴亚男,女,1957年生,讲师.

率为  $f_{\epsilon}$ ,被测频率为  $f_{\epsilon}$ ,其原理框图如图 1.

由框图知:(1)  $N \propto T$  或  $N \propto \frac{1}{f}$ ;

- (2)  $f_c \land$  测量准确度高;  $(T_x \mathbb{C} \text{时}, f_c \land \to N \land)$

- (3) N 的上限值受预置数限制,即  $N \leq$  预置数.

定标器由可预置计数器和算术运算电路组成,算术运算电路对输入 N 进行运算处理,输出  $10^{\circ}-N$  作为可预置计数器的预置数,该计数器在预置数的基础上对  $f_c$  计数. 如预置数为  $10^{\circ}-N$ ,则需 4 片可预置计数器(如 MN4029)和相应的算术运算电路.

仔细分析其工作原理,不难发现,定标器实质上是一个 N 进制计数器,其输入是  $f_c$ ,输出是  $f_c/N$ ,因为  $N=T_z/T_c=f_c/f_z$ ,所以,定标器输出是  $f_c/N=f_z$ .

$f_c = 常数, N \propto \frac{1}{f_c}$ ,即模随被测信号  $f_c$ 不同而不同. 如能设计一个模可变计数器,则电路要简单得多.

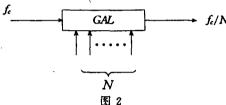

用 GAL 可以很方便地完成此项设计. 见图 2.

# 1 可重编程逻辑阵列

GAL 是 80 年代初研制出来的产品. 自 1986 年以来,通用可重编程逻辑阵列(GAL)以其高性能、高可靠性、可擦除及输出逻辑结构可组态的特性,赢得了广大用户的厚爱.

高性能、高可靠性体现在,设计师可以用 GAL 来实现各种需要的逻辑功能,简化系统设计,减少器件数量,提高系统可靠性.

所有 GAL 器件,在编程前,不具备任何逻辑功能.其输出采用逻辑宏单元(OLMC)形式, 正是由于 OLMC 的存在,我们可以自由设计、自由编程、灵活应用,使其具有某种特定的功能.

GAL 器件的基本类型有 16V8、20V8、39V8、和 ISP16Z8 等. GAL16V8 和 GAL20V8 的输出宏单元均为 8 个,外形为双列直插式.

借助于微机和 GAL 编程器,可以方便地对 GAL 进行编程,使其具有某种特定功能.

# 2 用 GAL16V8 设计模可变 N 进制计数器

设计思想:因为要求模 N 可在  $2\sim N_{\rm max}$ 间任意设定,所以  $N_{\rm max}$ 越大越好. 充分利用 GAL16V8 的 OLMC 单元,可以使  $N_{\rm max}$ 尽可能地大. GAL16V8 共有 8 个 OLMC,一个用作中间变量,一个用作外部输出(输出进位信号),还有 6 个 OLMC 可用作计数器,即  $N_{\rm max}=2^6=64$ ,一片 GAL16V8 可做 6 位模 64 计数器.

又要求模可在 2~64 间任意设定. 所以在 6 位模 64 计数器基础上必须增加一个模数控制

电路,用模数符合控制电路可满足此要求.

#### (1) 6 位模 64 计数器

写出状态激励表(表 1),通过卡诺图化简可得激励函数如下:

$$D_0 = \overline{Q}_1 \overline{Q}_0 + Q_1 \overline{Q}_0,$$

$$D_1 = Q_1 \overline{Q}_0 + \overline{Q}_2 \overline{Q}_1 Q_0 + Q_2 \overline{Q}_1 Q_0,$$

$$D_2 = Q_2 \overline{Q}_1 + \overline{Q}_2 Q_1 Q_0 + Q_2 Q_1 \overline{Q}_0,$$

$$D_3 = Q_3 \overline{Q}_2 + Q_3 \overline{Q}_1 + Q_3 Q_1 \overline{Q}_0 + \overline{Q}_3 Q_2 Q_1 Q_0$$

$$D_4 = Q_4 \overline{Q}_3 + Q_4 \overline{Q}_1 + Q_4 \overline{Q}_2 + Q_4 Q_1 \overline{Q}_0 + \overline{Q}_4 Q_3 Q_2 Q_1 Q_0,$$

$$D_{5} = Q_{5}\overline{Q}_{1} + Q_{5}\overline{Q}_{2} + Q_{5}Q_{1}\overline{Q}_{0} + Q_{5}\overline{Q}_{4} + Q_{5}Q_{4}\overline{Q}_{0} + \overline{Q}_{5}Q_{4}Q_{3}Q_{2}Q_{1}Q_{0}.$$

|            |       | •  |       |       | ~        |       |         |       |          |       |          |         |

|------------|-------|----|-------|-------|----------|-------|---------|-------|----------|-------|----------|---------|

| 时钟         |       | Į  | 见     | 7     | <u> </u> |       |         | ť     | <u>τ</u> | 7     | <u>z</u> |         |

| CP         | $Q_5$ | Q, | $Q_3$ | $Q_2$ | $Q_1$    | $Q_0$ | $D_{5}$ | $D_4$ | $D_3$    | $D_2$ | $D_1$    | $D_{o}$ |

| 1          | 0     | 0  | 0     | 0     | 0        | 0     | 0       | 0     | 0        | 0     | 0        | 1       |

| 2          | 0     | 0  | 0     | 0     | 0        | 1     | 0       | 0     | 0        | 0     | 1        | 0       |

| 3          | 0     | 0  | 0     | 0     | 1        | 0     | 0       | 0     | 0        | 0     | 1        | 1       |

| <b>:</b> . |       |    |       | :     |          |       |         |       | ,        | •     |          |         |

| 64         | 1     | 1  | 1     | 1     | 1        | 1     | 0       | 0     | 0        | 0     | 0        | 0       |

表 1 ·

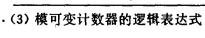

#### (2) 模数符合控制电路

计数器复位后,从"000000"开始计数. 当计数器状态  $Q_s \sim Q_o$  和模数控制输入信号 N=FEDCBA 不相符时,符合控制电路输出 T=0,计数器计数;当两者相符时,T=1,下一个计数脉冲使计数器回到"000000". T 同时可作为本计数器向高位发出的进位信号. 外加模数控制输入 FEDCBA 和计数器模的对应关系见表 2. 模数符合控制电路框图见图 3.

$$T = (F \oplus Q_5) + (E \oplus Q_4) + (D \oplus Q_3) + (C \oplus Q_2) + (B \oplus Q_1) + (A \oplus Q_0).$$

$$\stackrel{\cdot}{\mathcal{Z}} 2$$

|     |   |   |   |   |   | . <u> </u> |

|-----|---|---|---|---|---|------------|

| F   | E | D | С | В | A | 计数器模       |

| 0   | 0 | 0 | 0 | 0 | 0 | 不计数        |

| 0   | 0 | 0 | 0 | 0 | 1 | 模 2        |

| . 0 | 0 | 0 | 0 | 1 | 0 | 模 3        |

|     |   | : |   |   |   | :          |

| 1   | 1 | 1 | 1 | 1 | 1 | 模 64       |

|     |   |   |   |   |   |            |

将 6 位模 64 计数器和模数符合控制电路组合起来,求完整的逻辑表达式.根据设计要求,画出真值表如表 3.

由真值可写出模 0~64 之间可变计数器 的逻辑表达式:

$$Q_i = \overline{T}D_i, \qquad (i = 0 \sim 5)$$

| 输 | 入     | 输 出(状 态) |  |  |

|---|-------|----------|--|--|

| T | $D_i$ | $Q_i$    |  |  |

| 0 | $D_i$ | $D_i$    |  |  |

| 1 | $D_i$ | 0 -      |  |  |

速っ

将前面  $D_0 \sim D_5$  函数式代入上式,得完整逻辑表达式:

$$Q_0 = \overline{T}D_0 = \overline{T}(\overline{Q}_1\overline{Q}_0 + Q_1\overline{Q}_0),$$

$$Q_1 = \overline{T}D_1 = \overline{T}(Q_1\overline{Q}_0 + \overline{Q}_2\overline{Q}_1Q_0 + Q_2\overline{Q}_1Q_0),$$

$$Q_2 = \overline{T}D_2 = \overline{T}(Q_2\overline{Q}_1 + \overline{Q}_2Q_1Q_0 + Q_2Q_1\overline{Q}_0),$$

$$Q_3 = \overline{T}D_3 = \overline{T}(Q_3\overline{Q}_2 + Q_3\overline{Q}_1 + Q_3Q_1\overline{Q}_0 + \overline{Q}_3Q_2Q_1Q_0),$$

$$Q_4 = \overline{T}D_4 = \overline{T}(Q_4\overline{Q}_3 + Q_4\overline{Q}_1 + Q_4\overline{Q}_2 + Q_4Q_1\overline{Q}_0 + \overline{Q}_4Q_3Q_2Q_1Q_0),$$

$$Q_5 = \overline{T}D_5 = \overline{T}(Q_5\overline{Q}_1 + Q_5\overline{Q}_2 + Q_5Q_1\overline{Q}_0 + Q_5\overline{Q}_4 + Q_5Q_4\overline{Q}_0 + \overline{Q}_5Q_4Q_3Q_2Q_1Q_0),$$

$$\overline{T} = (F \oplus Q_5) + (E \oplus Q_4) + (D \oplus Q_3) + (C \oplus Q_2) + (B \oplus Q_1) + (A \oplus Q_9).$$

#### (4) 编写 PLD 源文件

由 GAL 的内部结构及时序工作方式所决定,或项至多为 7 项,所以必须引入中间变量 Z,同时将 T 函数式改写形式如下。

$$T = (F \oplus Q_5) + (E \oplus Q_4) + (D \oplus Q_3) + (C \oplus Q_2) + (B \oplus Q_4) + (A \oplus Q_0)$$

$$= F\overline{Q}_5 + \overline{F}Q_5 + E\overline{Q}_4 + \overline{E}Q_4 + D\overline{Q}_3 + \overline{D}Q_3 + C\overline{Q}_2 + \overline{C}Q_2 + B\overline{Q}_1 + \overline{B}Q_1 + A\overline{Q}_0 + \overline{A}Q_0,$$

$$\Leftrightarrow Z = \overline{D}Q_3 + C\overline{Q}_2 + \overline{C}Q_2 + B\overline{Q}_1 + \overline{B}Q_1 + A\overline{Q}_0 + \overline{A}Q_0,$$

则

$$T = F\overline{Q}_5 + \overline{F}Q_5 + E\overline{Q}_4 + \overline{E}Q_4 + D\overline{Q}_3 + Z.$$

PLD 源程序如下:

PLD16V8

MODE64

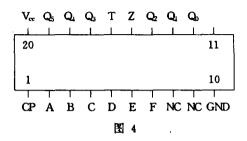

CLK A B C D E F NC NC GND

OE Q0 Q1 Q2 Z T Q3 Q4 Q5 VCC

$$Z = /D * Q3 + C * /Q2 + /C * Q2 + B * /Q1 + /B * Q1 + A * /Q0 + /A * Q0$$

$Z \cdot OE = VCC$

$/T = F * /Q5 + /F * Q5 + E * /Q4 + /E * Q4 + D * /Q3 + Z$

$T \cdot OE = VCC$

Q0: =  $/T * /Q1 * /Q0 + /T * Q1 * Q0$

Q1: =  $/T * Q1 * /Q0 + /T * /Q2 * /Q1 * Q0 + /T * Q2 * /Q1 * Q0$

Q2: =  $/T * Q2 * /Q1 + /T * /Q2 * Q1 * Q0 + /T * Q2 * Q1 * /Q0$

Q3 : = /T \* Q3 \* /Q2 + /T \* Q3 \* /Q1 + /T \* Q3 \* Q1 \* /Q0

+/T \*/Q3 \*Q2 \*Q1 \*Q0

$$Q4 : = /T * Q4 * /Q3 + /T * Q4 * /Q1 + /T * Q4 * /Q2 + /T * Q4 * Q1 * /Q0 + /T * /Q4 * Q3 * Q2 * Q1 * Q0$$

$$Q5: = /T * Q5 * /Q1 + /T * Q5 * /Q2 + /T * Q5 * Q1 * /Q0 + /T * Q5 * /Q4 + /T * Q5 * Q4 * /Q0 + /T * /Q5 * Q4 * Q3 * Q2 * Q1 * Q0$$

#### DISCREPTION

#### (5) 编程 GAL 器件

在微机上编辑好上述·PLD 文件后,运行专用编译软件,将源文件编译生成二进制代码的·JED 文件. 将 GAL 芯片锁定在 GAL 编程器上,再运行相应的编程软件(如 GP4A. EXE),即可对 GAL16V8 进行编程. 编程后该 GAL16V8 就是一片模 2~64 可变计数器了. 模数由FEDCBA 定,输出进位信号 T,器件的管脚分布见图 4.

# 4 结束语

实践证明,用 GAL16V8 编程的 6 位模 64 可变计数器,具有模数变化范围大,且设定方便的特点,适用于要求任意分频的场合,特别适合在工作过程中模随时变化的场合.用该计数器取代测周模式测频的定标器,在节省器件的同时,可以提高测量精度.

### 参考文献

- 1 蒋焕文等. 电子测量. 北京:中国计量出版社,1988

- 2 周南良. 数字逻辑. 长少:国防科大出版社,1992

- 3 丁嘉种等. 可编程逻辑器件 PLD. 北京:学苑出版社,1990

# Realization of a Variable Modulus Counter Via GAL16V8 Chips

Pei Yanan

Abstract

This thesis is about the frequency—surveying principle of cycle—surveying mode, and it also tells the fact that the counter of surveying mode and frequency should be taken the place by the desiger of GAL programming appliances and the changable counter of programming model.

Key words Counter; Modulus; Frequency